Register transfer

한학기동안 배울것

- 레지스터 종류와 쓰임 (하드웨어)

- 시퀀스 (소프트웨어)

- 컨트롤 (컨트롤)

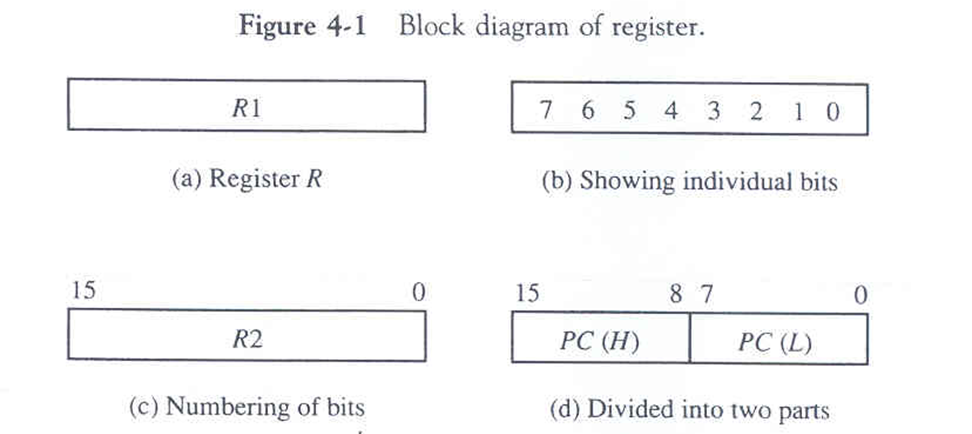

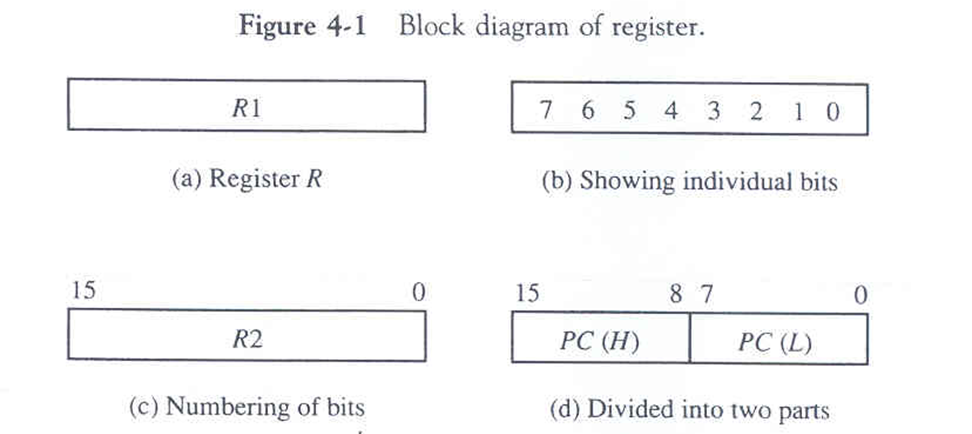

Block Diagram of Register

- AR (Address Register)

- DR(Data Register) or BR(Buffer Register)

- IR(Instruction Register)

- PC(Program Counter)

- R0 ~ R15 or A ~ H.

RTL, Basic symbols for register transfer

- Register-transfer level

- 하드웨어 레지스터 간의 디지털 신호 흐름과 해당 신호에 대해 수행되는 논리 연산 측면에서 동기식 디지털 회로를 모델링하는 설계 추상화입니다.

- Symbol: Microoperation을 활용한 데이터의 이동을 나타냄.

BUS

- A set of common lines

- Bus types:

- Address bus

- Data bus

- Control bus

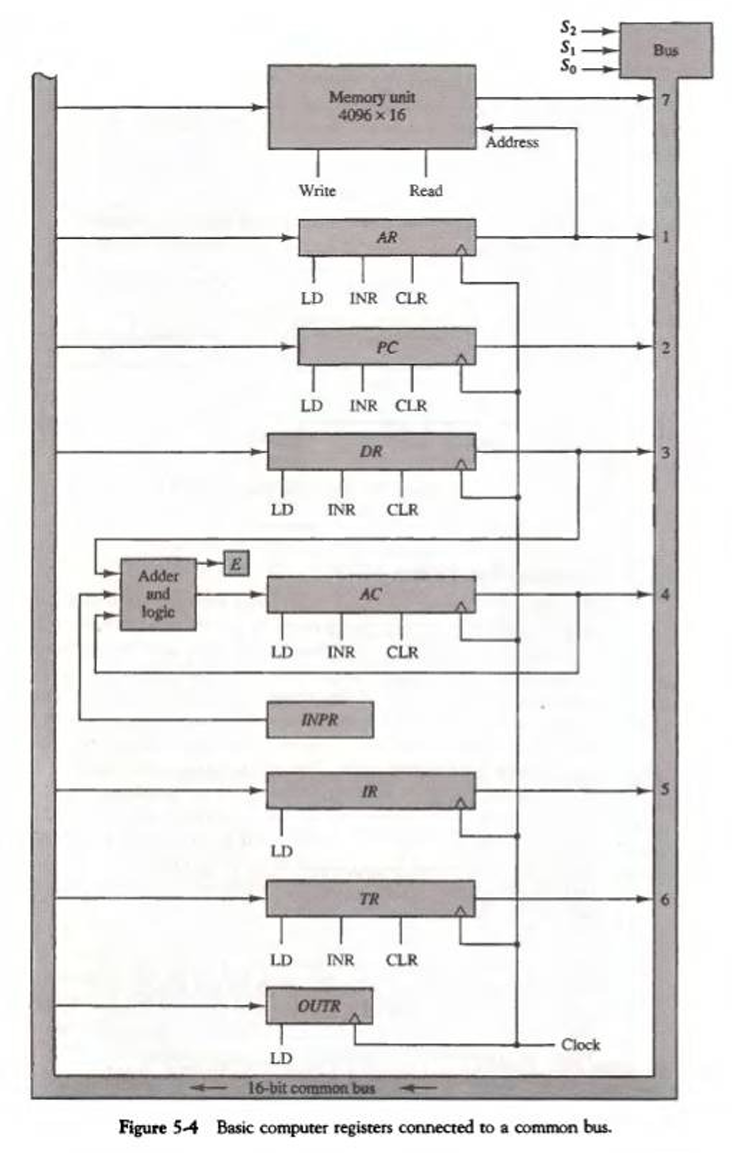

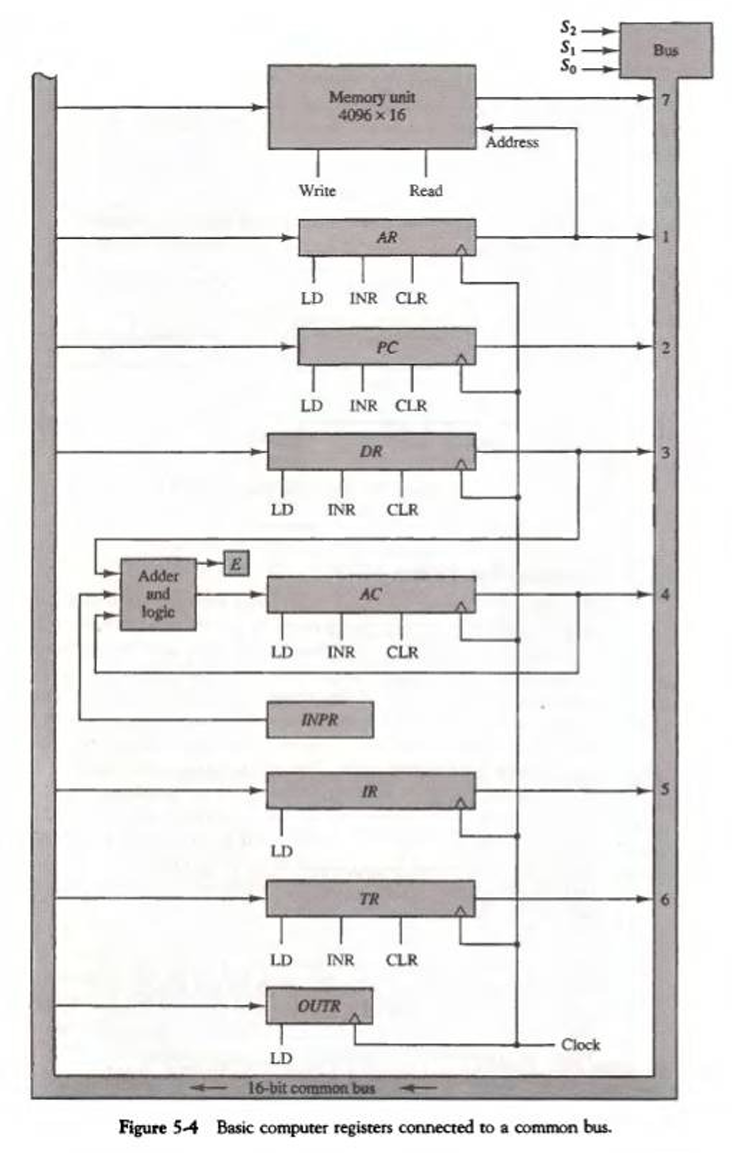

버스 예시 그림 (책 참고: Computer System Architecture - Morris Mano)

DR <- AC, AC <- DR 이때 버스는 누가 잡을까?

- Bypass라고, DR에서 AC로 이어지는 라인 때문에 동시상황일때 AC가 버스를 잡아야함.